# Bidirectional I<sup>2</sup>C Isolators

#### 1. General Description

The SiS154x devices are high reliability bidirectional isolators that are compatible with I<sup>2</sup>C interface. The SiS154x devices are safety, insulations withstand voltages (3.75kVrms, 5kVrms), while providing high electromagnetic immunity and low emissions at low power consumption. The I<sup>2</sup>C clock of the SiS154x is up to 1MHz, and the common-mode transient immunity (CMTI) is up to 150kV/us. Wide supply voltage of the SiS154x device support to connect with most digital interface directly, easy to do the level shift. High system level EMC performance enhances reliability and stability of use.

#### 2. Application

Power over Ethernet

- level shifting

- SMBus, or PMBus interface

- Isolated I<sup>2</sup>C buses

- Power over Ethernet

- BMS

#### 3. Feature

- Bidirectional communication

- Open Drain Output

- With 3.5-mA Side 1 and 30- mA Side 2 sink current capability

- I<sup>2</sup>C Clock rate: up to 1MHz

- Hot swap protection

- Power supply voltage: 3.0V to 5.5V

- Support different supply voltage in primary side and secondary side.

- CMTI :100kV/us

- Operation temperature: –40°C to +125°C

- Safety certifications:

- 3.75kV<sub>RMS</sub> isolation for SOP8 package

- 5kV<sub>RMS</sub> isolation for SOW8 package

#### 4. Device Information

|   | Part Number | Package  | Body Size(NOM)        |  |  |

|---|-------------|----------|-----------------------|--|--|

|   | SiS1540S    | (C) COD0 | 4.90mm × 3.90mm       |  |  |

|   | SiS1541S    | (S) SOP8 |                       |  |  |

| Ī | SiS1540G    | (C) COMO | F 05 mans v 7 50 mans |  |  |

|   | SiS1541G    | (G) SOW8 | 5.85mm × 7.50mm       |  |  |

5. Ordering Information

| Part Number | Marking | Bidirectional<br>Channel | Unidirectional<br>Channel | Isolation<br>Rating(kV <sub>RMS</sub> ) | Package | Packing Form         |  |

|-------------|---------|--------------------------|---------------------------|-----------------------------------------|---------|----------------------|--|

| SiS1540S    | iS1540S | 2                        | 0                         | 3.75                                    | SOP8    | 0000:                |  |

| SiS1541S    | iS1541S | 1                        | 1                         | 3.75                                    | 30P6    | 3000 pieces per reel |  |

| SiS1540G    | iS1540G | 2                        | 0                         | F 0                                     | SOW8    | 1000 min and man mad |  |

| SiS1541G    | iS1541G | 1                        | 1                         | 5.0                                     | 3000    | 1000 pieces per reel |  |

6. Absolute Maximum Ratings

| Absolu              | te maximum natim                     | ၝ၁         |      |                           |      |

|---------------------|--------------------------------------|------------|------|---------------------------|------|

|                     |                                      |            | MIN  | MAX                       | UNIT |

|                     | Voltage                              | Vcc1, Vcc2 | -0.5 | +6.0                      |      |

|                     |                                      | SDA1, SCL1 | -0.5 | Vcc1 + 0.5 <sup>(3)</sup> | V    |

|                     |                                      | SDA2, SCL2 | -0.5 | Vcc2 + 0.5 <sup>(3)</sup> |      |

|                     | Output current SDA1, SCL1 SDA2, SCL2 | SDA1, SCL1 | -18  | 18                        | A    |

| Io                  |                                      | -100       | 100  | mA                        |      |

| T <sub>J(MAX)</sub> | Maximum junction temper              | erature    |      | 150                       | °C   |

| T <sub>stg</sub>    | Storage temperature                  |            | -40  | 150                       | °C   |

www.SyntoneMicro.com 1/9 Ver0.90 Jan,2025

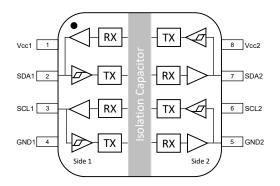

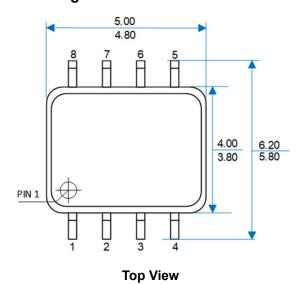

# Pin Configuration and Functions SiS1540 SOIC-8 / SOIC-8W Top View

#### Pin Functions -- SiS1540 Name **Description**` Pin No. Vcc1 1 Supply voltage, side1 2 SDA1 Serial date input / output, side 1 3 SCL1 Serial clock input / output, side 1 4 GND1 Ground, side 1 5 GND2 Ground, side 2 6 SCL2 Serial clock input / output, side 2 7 SDA2 Serial date input / output, side 2 8 Vcc2 Supply Voltage, side 2

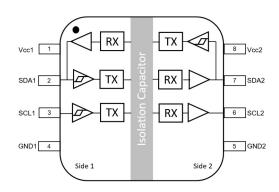

#### SiS1541 SOIC-8 / SOIC-8W Top View

| Pin Functions SiS1541 |      |                                    |  |  |  |  |

|-----------------------|------|------------------------------------|--|--|--|--|

| Pin No.               | Name | Description                        |  |  |  |  |

| 1                     | Vcc1 | Supply voltage, side1              |  |  |  |  |

| 2                     | SDA1 | Serial date input / output, side 1 |  |  |  |  |

| 3                     | SCL1 | Serial clock input, side 1         |  |  |  |  |

| 4                     | GND1 | Ground, side 1                     |  |  |  |  |

| 5                     | GND2 | Ground, side 2                     |  |  |  |  |

| 6                     | SCL2 | Serial clock output, side 2        |  |  |  |  |

| 7                     | SDA2 | Serial date input / output, side 2 |  |  |  |  |

| 8                     | Vcc2 | Supply Voltage, side 2             |  |  |  |  |

<u>www.SyntoneMicro.com</u> **2 / 9** Ver0.90 Jan,2025

# 8. Recommended Operating Conditions

|                                       |                                          | MIN        | MAX        | UNIT |

|---------------------------------------|------------------------------------------|------------|------------|------|

| Vcc1, Vcc2                            | Supply voltage                           | 3.0        | 5.5        | V    |

| V <sub>SDA1</sub> , V <sub>SCL1</sub> | Input and output signal voltages, side 1 | 0          | Vcc1       | V    |

| V <sub>SDA2</sub> , V <sub>SCL2</sub> | Input and output signal voltages, side 2 | 0          | Vcc2       | V    |

| V <sub>IL1</sub>                      | Low-level input voltage, side 1          | 0          | 0.5        | V    |

| V <sub>IH1</sub>                      | High-level input voltage, side 1         | 0.7 × Vcc1 | Vcc1       | V    |

| V <sub>IL2</sub>                      | Low-level input voltage, side 2          | 0          | 0.3 × Vcc2 | V    |

| V <sub>IH2</sub>                      | High-level input voltage, side 2         | 0.7 × Vcc2 | Vcc2       | V    |

| I <sub>OL1</sub>                      | Output current, side 1                   | 0.5        | 3          | mA   |

| I <sub>OL2</sub>                      | Output current, side 2                   | 0.5        | 30         | mA   |

| CL1                                   | Capacitive load, side 1                  |            | 40         | pF   |

| CL2                                   | Capacitive load, side 2                  |            | 400        | pF   |

| T <sub>A</sub>                        | Ambient temperature                      | -40        | 125        | °C   |

#### 9. Electrical Characteristics

over recommended operating conditions, unless otherwise noted

|                                                                                                            | PARAMETER                                                 | TEST CONDITIONS                                                          | MIN        | TYP  | MAX        | UNIT |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------|------------|------|------------|------|

| SIDE 1                                                                                                     | (ONLY)                                                    |                                                                          |            |      | ·          |      |

| V <sub>ILT1</sub>                                                                                          | Voltage input threshold low,<br>SDA1 and SCL1             |                                                                          | 500        |      | 700        | mV   |

| $V_{\text{IHT1}}$                                                                                          | Voltage input threshold high,<br>SDA1 and SCL1            |                                                                          | 500        |      | 700        | mV   |

| $V_{HYST1}$                                                                                                | Voltage input hysteresis                                  | V <sub>IHT1</sub> –V <sub>ILT1</sub>                                     | 50         |      |            | mV   |

| $V_{OL1}$                                                                                                  | Low-level output voltage,<br>SDA1 and SCL1 <sup>(1)</sup> | $0.5 \text{ mA} \le (I_{SDA1} \text{ and } I_{SCL1}) \le 3.0 \text{ mA}$ | 600        |      | 900        | mV   |

| Low-level output voltage to high level input voltage threshold difference, SDA1 and SCL1 <sup>(1)(2)</sup> |                                                           | 0.5 mA ≤ (I <sub>SDA1</sub> and I <sub>SCL1</sub> ) ≤ 3.0 mA             | 50         |      |            | mV   |

| SIDE 2                                                                                                     | (ONLY)                                                    |                                                                          |            |      |            |      |

| $V_{\text{ILT2}}$                                                                                          | Voltage input threshold low,<br>SDA2 and SCL2             |                                                                          |            |      | 0.3 × Vcc2 | V    |

| V <sub>IHT2</sub>                                                                                          | Voltage input threshold high,<br>SDA2 and SCL2            |                                                                          | 0.7 × Vcc2 |      |            | V    |

| V <sub>OL2</sub>                                                                                           | Low-level output voltage,<br>SDA2 and SCL2                | 0.5 mA ≤ (I <sub>SDA2</sub> and I <sub>SCL2</sub> ) ≤ 35 mA              |            |      | 0.4        | V    |

| вотн ѕ                                                                                                     | SIDES                                                     |                                                                          |            |      |            |      |

| ΙΙ <sub>L</sub> Ι                                                                                          | Input leakage currents, SDA1,<br>SCL1, SDA2, and SCL2     | $V_{SDA1}$ , $V_{SCL1}$ = $Vcc1$ ; $V_{SDA2}$ , $V_{SCL2}$ = $Vcc2$      |            | 0.01 | 10         | μА   |

| lcc1                                                                                                       | Supply current, side 1                                    | 4.5 V ≤ Vcc1, Vcc2 ≤ 5.5 V                                               |            |      | 12         | mA   |

| Icc2                                                                                                       | Supply current, side 2                                    | 4.5 V ≤ Vcc1, Vcc2 ≤ 5.5 V                                               |            |      | 12         | mA   |

| lcc1                                                                                                       | Supply current, side 1                                    | 3.0V ≤ Vcc1, Vcc2 ≤ 3.6V,                                                |            |      | 12         | mA   |

| lcc2                                                                                                       | Supply current, side 2                                    | 3.0V ≤ Vcc1, Vcc2 ≤ 3.6V,                                                |            |      | 12         | mA   |

| CMTI                                                                                                       | Common-mode transient immunity                            | CM <sub>H</sub>                                                          | 25         | 35   |            | kV/u |

www.SyntoneMicro.com 3 / 9 Ver0.90 Jan,2025

#### 10. Thermal Information

| THERMAL METRIC  |                                        | S(SOP8) | G(SOW8) | UNIT |

|-----------------|----------------------------------------|---------|---------|------|

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 110     | 92.5    | °C/W |

## 11. Switching Characteristics

over recommended operating conditions, unless otherwise noted

| PARAMETER                          |                                                                    | TEST C                                                       | TEST CONDITIONS           |  | TYP | MAX  | UNIT |

|------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|--|-----|------|------|

|                                    | Frequency                                                          |                                                              |                           |  |     | 1000 | kHz  |

|                                    |                                                                    |                                                              |                           |  |     |      |      |

| t <sub>f1</sub>                    | Output Signal Fall<br>Time (SDA1, SCL1)                            | R1 = 1.6kΩ, C1 = 40 pF                                       | 0.9 × Vcc1 to 900 mV      |  | 14  | 120  | ns   |

| t <sub>f2</sub>                    | Output Signal Fall<br>Time (SDA2, SCL2)                            | R2 = 180 Ω, C2 = 400 pF                                      | 0.9× Vcc2 to 0.1 × Vcc2   |  | 30  | 120  | ns   |

| 3.0V≤Vcc1,                         | Vcc2≤3.6V                                                          |                                                              |                           |  |     |      |      |

| t <sub>f1</sub>                    | Output Signal Fall Time<br>(SDA1, SCL1)                            | R1 = 1.0kΩ, C1 = 40 pF                                       | 0.9 × Vcc1 to 900 mV      |  | 14  | 120  | ns   |

| t <sub>f2</sub>                    | Output Signal Fall Time (SDA2, SCL2)                               | R2 = 120 Ω, C2 = 400 pF                                      | 0.9× Vcc2 to 0.1 × Vcc2   |  | 32  | 120  | ns   |

| PROPAGAT                           | ΓΙΟΝ DELAY                                                         |                                                              |                           |  |     |      |      |

| t <sub>PLH1-2</sub>                | Low-to-High Propagation<br>Delay, Side 1 to Side 2                 |                                                              | 0.5 × Vcc1 to 3.5V        |  | 48  | 130  | ns   |

| t <sub>PHL1-2</sub>                | High-to-Low Propagation Delay, Side 1 to Side 2                    |                                                              | 0.5 × Vcc1 to 0.4 V       |  | 50  | 275  | ns   |

| PWD <sub>1-2</sub>                 | Pulse Width Distortion                                             | 4.5V ≤ Vcc1,<br>Vcc2 ≤ 5.5V.                                 |                           |  | 30  | 145  | ns   |

| t <sub>PLH2-1</sub> (1)            | Low-to-High Propagation Delay, Side 2 to Side 1                    | R1 = 1.6kΩ,<br>R2 = 180Ω,                                    | 0.4 × Vcc2 to 0.7 × Vcc1  |  | 63  | 130  | ns   |

| t <sub>PHL2-1</sub> (1)            | High-to-Low Propagation Delay, Side 2 to Side 1                    | - C1 = C2 = 0pF                                              | 0.4 × Vcc2 to 0.9 V       |  | 18  | 155  | ns   |

| PWD <sub>2-1</sub>                 | Pulse Width Distortion                                             |                                                              |                           |  | 54  | 85   | ns   |

| t <sub>PLH1-2</sub>                | Low-to-High Propagation Delay, Side 1 to Side 2                    |                                                              | 0.50 × Vcc2 to 0.7 × Vcc2 |  | 65  | 125  | ns   |

| t <sub>PHL1-2</sub>                | High-to-Low Propagation Delay, Side 1 to Side 2                    |                                                              | 0.70 to 0.4V              |  | 67  | 340  | ns   |

| PWD <sub>1-2</sub>                 | Pulse Width Distortion   t <sub>PLH1-2</sub> - t <sub>PHL1-2</sub> | 3.0V ≤ Vcc1,<br>Vcc2 ≤ 3.6V,                                 |                           |  | 25  | 215  | ns   |

| t <sub>PLH2-1</sub> <sup>(1)</sup> | Low-to-High Propagation Delay, Side 2 to Side 1                    | R1 = $1.0k\Omega$ ,<br>R2 = $120\Omega$ ,<br>C1 = C2 = $0pF$ | 0.50 × Vcc2 to 0.7 × Vcc1 |  | 68  | 130  | ns   |

| t <sub>PHL2-1</sub> <sup>(1)</sup> | High-to-Low Propagation Delay, Side 2 to Side 1                    |                                                              |                           |  | 23  | 210  | ns   |

| PWD <sub>2-1</sub>                 | Pulse Width Distortion   t <sub>PLH2-1</sub> - t <sub>PHL2-1</sub> |                                                              |                           |  | 34  | 135  | ns   |

www.SyntoneMicro.com 4/9 Ver0.90 Jan,2025

#### 12. ESD Ratings and V<sub>ISO</sub>

| PARAMETER          |                             | TEST CONDITIONS                                                                                                                                |          | VALUE |       | UNIT      |

|--------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------|-----------|

|                    |                             | TEST CONDITIONS                                                                                                                                |          |       | G     |           |

| V <sub>(ESD)</sub> | Electrostatic               |                                                                                                                                                | Bus pins | ±8000 | ±8000 |           |

|                    |                             |                                                                                                                                                | All pins | ±4000 | ±4000 |           |

| discharge          |                             | Charged-device model (CDM), per JEDEC specification                                                                                            |          | ±2000 | ±2000 | V         |

|                    |                             | Machine Model JEDEC JESD22-A115-A, all pins                                                                                                    |          | ±200  | ±200  |           |

| V <sub>ISO</sub>   | Withstand isolation voltage | $V_{TEST} = V_{ISO} = 2500 V_{RMS}$ , $t = 60 s$ (qualification); $V_{TEST} = 1.2 \times V_{ISO} = 3000 V_{RMS}$ , $t = 1 s$ (100% production) |          | 3750  | 5000  | $V_{RMS}$ |

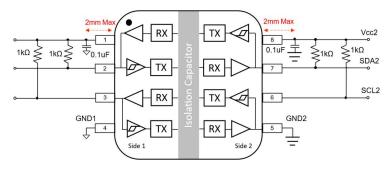

#### 13. Parameter Measurement Information

Test Circuit of SiS154x

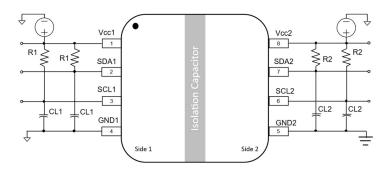

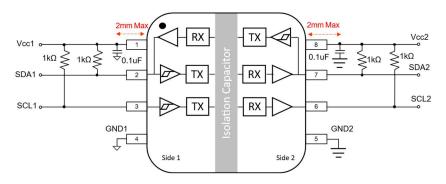

#### 14. Typical Application

The SiS1540 and SiS1541 isolation ICs provide complete galvanic isolation between two power domains, protecting circuits from high common-mode transients and faults, eliminating ground loops. These devices do not require special power-supply sequencing, the logic levels are set independently on either side by Vcc1 and Vcc2. The SDA1, SCL1, SDA2, SCL2 pins have open-drain outputs, requiring pull-up resistors to their respective supplies for logic-high outputs. The output low voltages are guaranteed for sink currents of up to 35mA for side B, and 3.5mA for side 1. So the minimum pullup resistors on the input lines must be selected in such a way that input current drawn is  $\leq$  3.5mA on side 1 and output current drawn is  $\leq$  35mA on side B. The maximum pull-up resistors on the input lines and output lines depend on the load and rise time requirements on the respective lines. To reduce ripple and the chance of introducing data errors, bypass Vcc1 and Vcc2 with at least  $0.1\mu F$  low-ESR ceramic capacitors to GND1 and GND2 respectively. Place the bypass capacitors as close to the power supply input pins as possible.

To reduce ripple and the chance of introducing data errors, bypass Vcc1 and Vcc2 with at least  $0.1\mu F$  low-ESR ceramic capacitors to GND1 and GND2 respectively. Place the bypass capacitors as close to the power supply input pins as possible.

• Typical Application Circuit of SiS1540

www.SyntoneMicro.com 5 / 9 Ver0.90 Jan,2025

Typical Application Circuit of SiS1541

www.SyntoneMicro.com 6 / 9 Ver0.90 Jan,2025

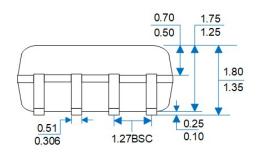

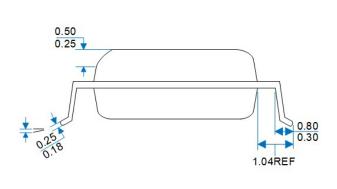

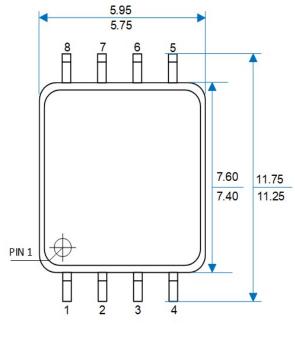

#### 15. Package Outlines: SOP8

Side View 1

Side View 2

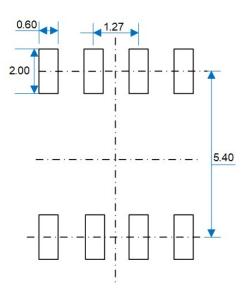

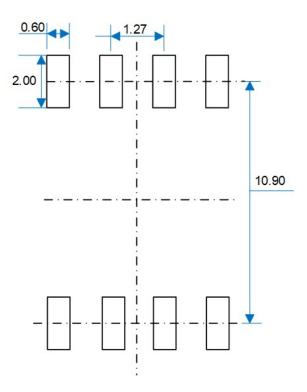

**Recommended Land Pattern**

www.SyntoneMicro.com 7/9 Ver0.90 Jan,2025

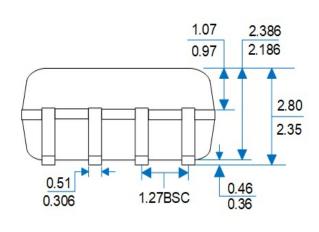

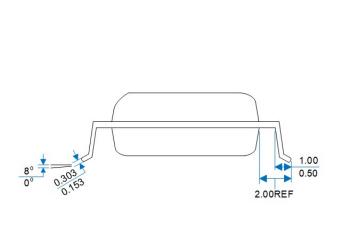

### 16. Package Outlines: SOW8

**Top View**

Side View 1

Side View 2

**Recommended Land Pattern**

www.SyntoneMicro.com 8/9 Ver0.90 Jan,2025

#### Disclaim

All product specifications and data are subject to change without notice.

For documents and material available from this datasheet, Syntone Microsystems does not warrant or disclosed hereunder.

No license, express or implied, by estoppels or otherwise, to any intellectual property rights is granted by this document or his document or by any conduct of Syntone Microsystems.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless. Customers using or selling Syntone Microsystems products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Syntone Microsystems for any damages arising or resulting from such use or sale. Syntone Microsystems disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Syntone Microsystems' terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

Syntone Microsystems strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

In the event that any or all Syntone Microsystems products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

www.SyntoneMicro.com 9 / 9 Ver0.90 Jan,2025